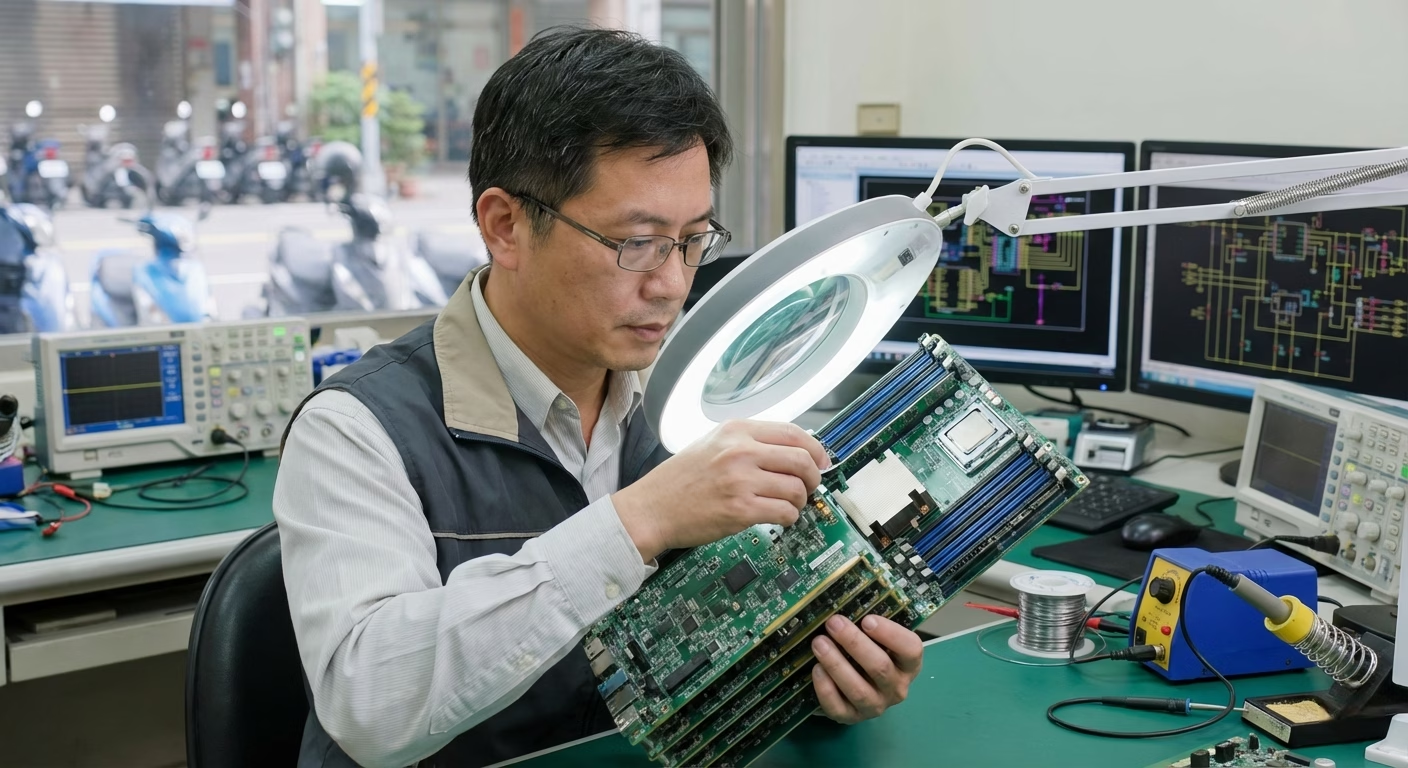

在 5G/6G 通訊與高效能運算 (HPC) 系統設計中,RF/天線工程師與 SI/PI 專家面臨著前所未有的挑戰:隨著 PCB 層數與走線密度的極致壓縮,將求解時間以「週」計算的電磁模擬,已成為阻礙產品上市的巨大瓶頸。本篇技術專文將從專業顧問的視角,探討大尺度全板萃取所面臨的運算極限,並深入剖析如何透過演算法與架構的革新,徹底解決工程師的效能焦慮。

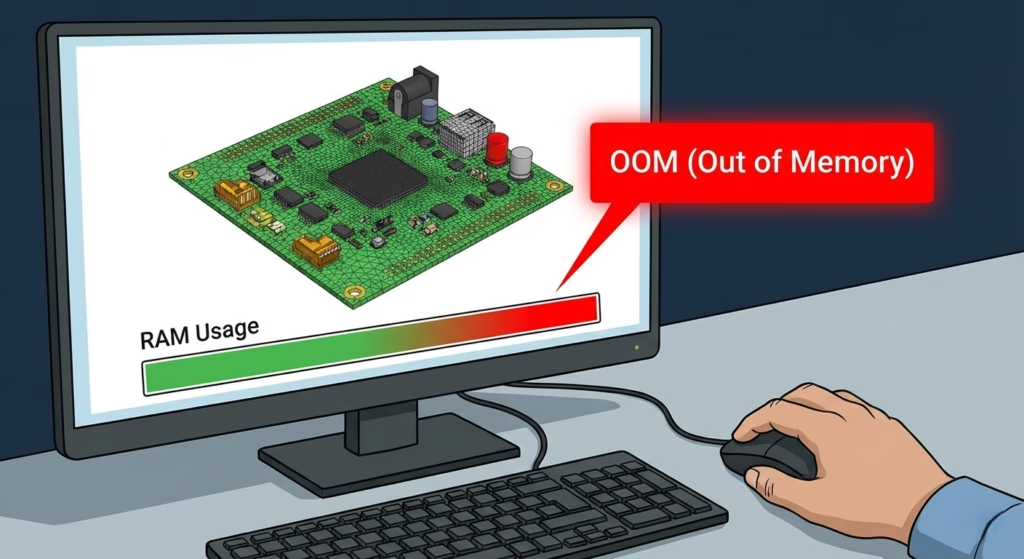

物理限制與維度災難:剖析全板萃取 OOM (Out of Memory) 的底層邏輯

若我們進一步拆解大尺度 PCB 模擬的本質困難,問題的癥結在於「空間離散化與矩陣求解」的數學物理限制。

傳統的 3D 全波電磁求解器(多數採用頻域的有限元素法 FEM)在處理全板複雜幾何時,必須將空間劃分為極大量的網格。根據數值分析理論,其剛性矩陣 (Stiffness Matrix) 的規模將隨網格數量 N 呈 O(N2) 甚至 O(N3) 的非線性暴增。這意味著,當電路板尺寸擴大或頻率升高導致網格激增時,所需的記憶體容量將呈幾何級數飆升(即所謂的「維度災難」)。

我們必須理性認知:單純依賴升級單機 RAM 是一種極低投資回報率 (ROI) 的策略。因為硬體的擴增速度,永遠趕不上高頻演算法矩陣膨脹的規模。這正是傳統軟體在進行高密度互連 (HDI) 或先進封裝模擬時,全板萃取 OOM (Out of Memory) 必然發生的根本原因。

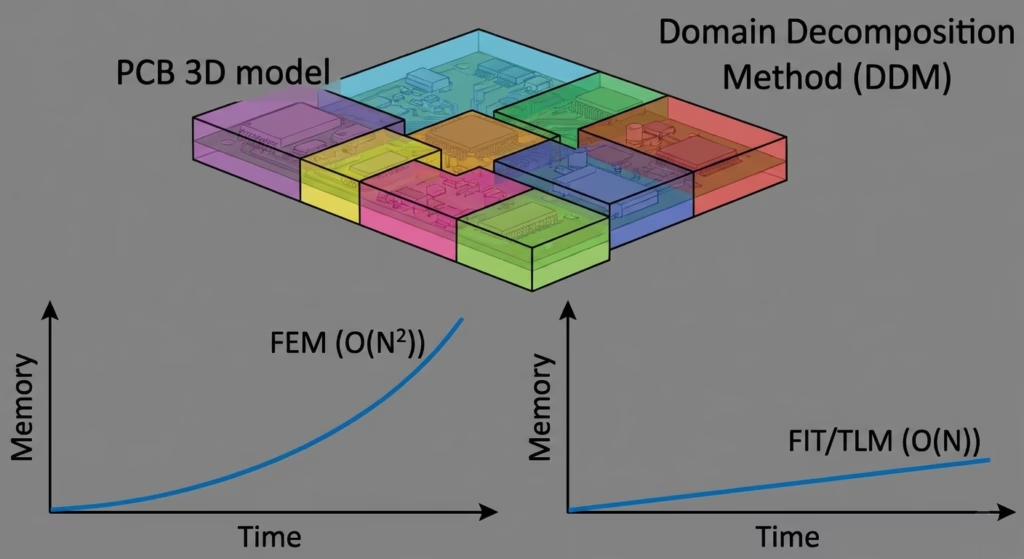

演算法重構:突破 3D EM 求解器記憶體溢出的區域分解技術 (DDM)

要突破此一瓶頸,必須從數值分析專家的視角,進行「演算法層面」的重構。與競品重度依賴單一頻域 FEM 演算法不同,現代化的解決方案如 SIMULIA CST 採用了更具彈性的混合架構,其中包含兩大核心破局技術:

- 時間域 FIT/TLM 演算法的線性優勢:不同於 FEM 求解矩陣的 O(N2) 記憶體消耗,CST 核心的有限積分法 (FIT) 與傳輸線矩陣法 (TLM) 在時間域的記憶體消耗隨網格數呈線性 O(N) 增長。這表示在處理相同的巨型 PCB 時,CST 先天具備極高的記憶體使用效率。

- 區域分解技術 (Domain Decomposition Method, DDM):面對極端龐大且無法由單一節點求解的全板模型,DDM 技術能將其精確切割為多個可獨立運算且邊界連續的子區域 (Sub-domains)。

透過理論證實與實務驗證,結合 O(N) 的時域演算法與 DDM 分割,此架構能有效規避 3D EM 求解器記憶體溢出 的風險,同時透過嚴謹的邊界條件交換,維持高置信度的全局模擬精度。這也是為何 CST 能夠將原本需要數週的運算,穩定壓縮至數天甚至數小時的關鍵。

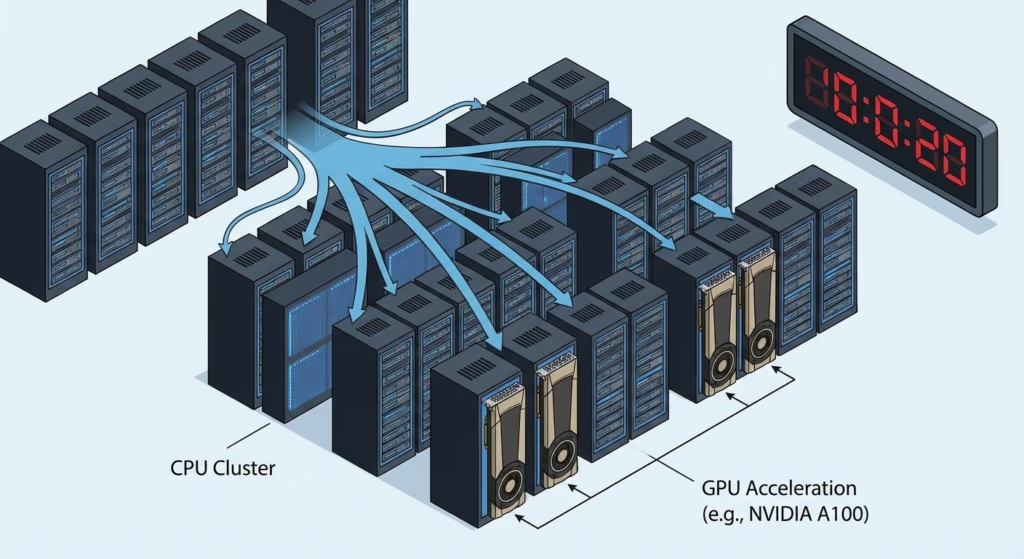

硬體與算力解耦:分散式運算重塑系統級電磁模擬效能

演算法的突破,為企業 IT 基礎設施的架構轉型提供了基礎。大尺度全板萃取不再受限於單一超級電腦,而是透過硬體與算力的解耦,走向分散式運算。

透過 MPI(訊息傳遞介面)與 HPC(高效能運算)叢集技術,CST 能夠將 DDM 切割後的運算任務,高效分散至多個節點(Nodes)執行。針對硬體架構的投資,我們提供以下置信度評估:

- 多核心 CPU 叢集(高置信度投資):對於擁有大量 RAM 需求的全板模型,橫向擴充 CPU 節點能提供極高的穩定性與線性加速比,實質提升 系統級電磁模擬效能。

- GPU 硬體加速(中/高置信度投資):針對時域 (Time Domain) 演算法,高階 GPU (如 NVIDIA A100/H100) 龐大的浮點運算力與超高記憶體頻寬,能在單一節點內爆發出相當於數十顆 CPU 的求解速度,是追求極致加速的首選配置。

降階模型與自適應網格:實現 PCB 全板模擬加速的雙引擎

從 SI/PI 工程師的實務視角出發,在求解引擎之外,前處理與網格生成更是決定記憶體消耗的關鍵戰場。以下兩大技術被視為實現 PCB 全板模擬加速 的雙引擎:

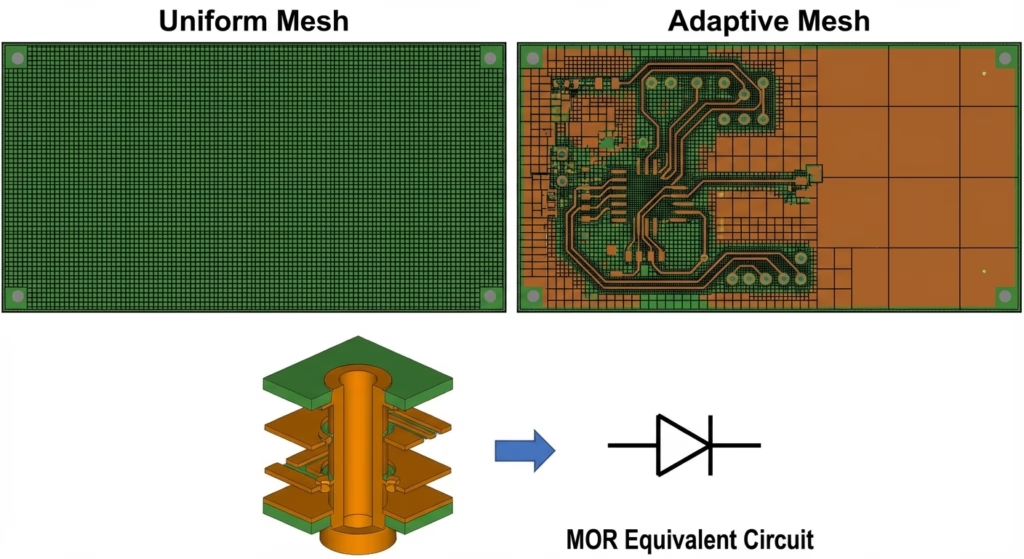

- 智慧型自適應網格技術 (Adaptive Meshing):摒棄傳統全域均勻切割的浪費,系統能針對高頻訊號走線密集區、過孔 (Via) 與不連續點自動加密網格,而在平坦的鋪銅區維持較粗網格。此舉可在不損失運算精度的前提下,大幅縮減總網格數。

- 模型降階技術 (Model Order Reduction, MOR):將複雜的 3D 電磁結構萃取為等效的寬頻 SPICE 電路模型或 S 參數黑盒子。這使得龐大的 3D 結構能夠降階融入系統級電路模擬中,在運算精度與記憶體消耗之間取得物理與數學上的最佳平衡點。

導入新世代運算架構的風險與收益

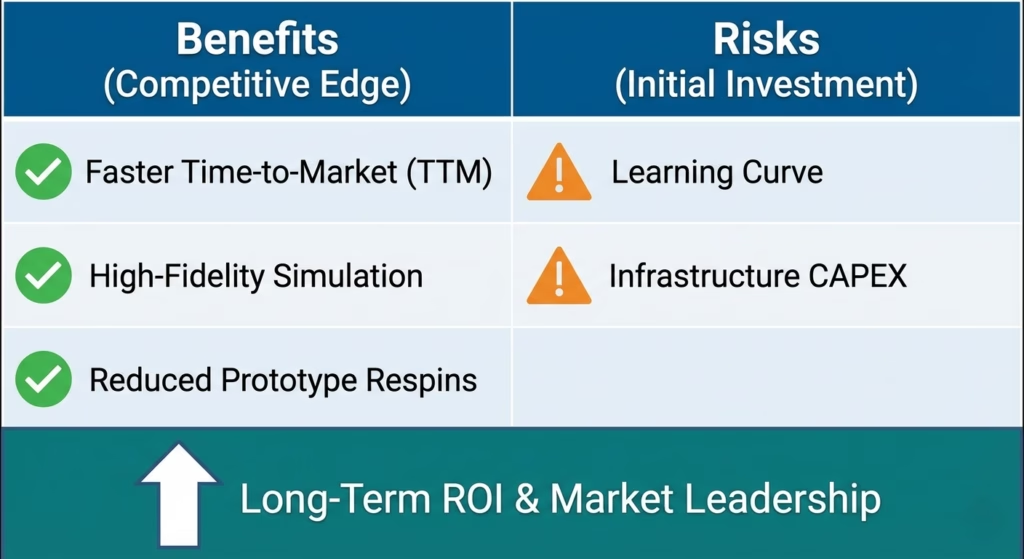

綜合上述多方視角,若企業欲導入以 SIMULIA CST 為核心的新世代全板模擬架構,我們採用批判性評估(Critical Evaluation)模型提供以下戰略建議:

| 評估面向 | 說明與置信度分析 |

|---|---|

| 優勢 (效益) | 徹底打破驗證盲區:能以高置信度執行全板 SI/PI/EMI 聯合模擬,精準捕捉跨區域的串擾 (Crosstalk) 與諧振,大幅減少產品原型打樣與改版次數 (Respins)。運算時間壓制:將傳統 FEM 競品以「週」為單位的求解時間,降維打擊至以「天」或「小時」計。 |

| 劣勢 (風險) | 學習曲線與過渡期:從傳統頻域思維轉換至時域與 DDM 混合架構,團隊在初期需要克服一定的軟體操作學習曲線。基礎設施重構:發揮最大效能需要相應的 HPC 叢集或高階 GPU 投資,初期具備一定的資本支出 (CAPEX) 門檻。 |

結論

在先進封裝與高頻高速系統設計的賽道上,掌握大尺度全板萃取能力,已非單純的工程優化,而是企業維持市場競爭力、確保產品準時交付 (TTM) 的必經之路。

如果您與您的團隊也正深陷於求解器無窮無盡的等待,甚至頻繁遭遇記憶體溢出 (OOM) 的挫敗中,請立即審視現有的工具鏈。歡迎深入了解並體驗 SIMULIA CST 的卓越運算架構,透過時域演算法與區域分解技術 (DDM) 的強大威力,讓您的系統級模擬重拾流暢效能,贏得市場先機。